# PWM of Cascaded Five level Voltage Source Inverter using FPGA

## N. Rajavinu<sup>1</sup>

Abstract - Multilevel inverter technology has emerged recently as a very important alternative in the area of high-power medium-voltage energy control. Various topologies of multilevel inverter provides several advantages including lower voltage stress, higher efficiency, lower electromagnetic interference. To obtain a quality output voltage with minimum amount of ripple content, they require high switching frequency along with advance pulse width modulation strategies. As a result, a multilevel power inverter structure has been introduced as an alternative in high power applications. This paper presents single phase cascaded five level inverter with separate dc sources. Cascaded multilevel inverter constructed by two full Hbridges. FPGA is chosen for the hardware implementation of switching strategy mainly due to its high computation speed that can ensure the accuracy of the instants that gating signals are generated. VHDL language is used to model the inverter switching strategies.

Index Terms - Cascaded H-bridge multilevel inverter, digital pulse width modulation(DPWM), field programming gate array(FPGA).

## **I.INTRODUCTION**

Multilevel inverters have been attracting increasing attention in the past few years as power converters of choice in many applications. They have significant advantages over the conventional one because of the capability to reduce the undesirable harmonics in order to improve the performance and efficiency. It may be easier to produce a high power and high voltage inverter with multilevel structure because of the way in which device voltage stresses are controlled in structure.

Multilevel inverters are significantly different from the ordinary inverter where only two levels are generated. In which each group of devices contribute to a step in the output voltage waveform. The steps are increased to obtain an almost sinusoidal waveform. The number of switches involved is increased for every level increment. Generally the output waveform of the multilevel inverter is generated from different voltage sources obtained from the capacitor voltage sources. In the past two decades, several multilevel voltage source Multilevel Inverter for Single Phase System with Reduced Number of Switches converters have been introduced. The various topological structures of the multilevel inverter suggestions must cope with The following points: 1) less number of switching devices, 2) capable of enduring high voltage and high power, and 3) lower switching frequency for the switching devices. Cascaded H-bridge multilevel inverter is gaining faster development due to its topological and modularity significance.[1-3].

Ordinary PWM modulation for two-level inverters is accomplished through comparison between a reference wave and a triangular carrier wave. The reference wave have the frequency and amplitude wanted for the output voltage signal and the triangular carrier wave has the amplitude of half the DC input voltage, in an simple ordinary case, and its frequency is dependent on application but must be higher than the reference wave frequency.

Digital PWM generation is considered as an alternate modulation technique in place of the conventional sinusoidal PWM using triangular carriers for the multilevel inverter operation that has the advantages of implementation simplicity and possibility to reduce harmonic distortions. Some methods us carrier disposition and others use phase shifting of the multiple carrier signals. Digital controllers, such as microprocessors, DSP, FPGA and application specific integrated circuits (ASIC) are gaining importance in the power electronics applications as they can easily implement DPWM, with better performance and at low cost [4-8]. Therefore, digital control techniques are becoming more common solutions in modem power converters.Field Programmable Gate Array (FPGA) offers the most preferred way of designing PWM Generator for Power Converter Applications. FPGA is only an array of gate that can be connected as the user wishes. FPGA are used for relatively simpler operations but higher processing speed in comparison to microcontrollers. In the last few years, the field programmable gate array (FPGA) circuits have become popular in the applications where high performance, low development, low production cost and fast time-to market are required. We have to just change the interconnection between these logic blocks. This feature of reprogramming capability of FPGA makes it suitable to make your design using FPGA. Also using FPGA we can implement design within a short time and efficient hardware for rapid prototyping. Thus FPGA is the best way of designing digital PWM Generators. Also implementation of FPGA-based control schemes proves less costly and hence they are economically suitable for small designs.

## II. OPERATION OF FIVE LEVEL CASCADED H-BRIDGE INVERTER

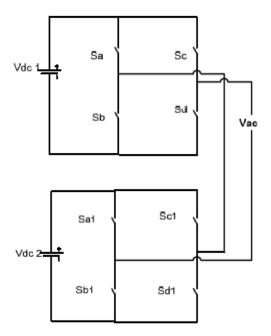

The cascaded H-bridge multilevel inverter circuit is shown in Fig. 1. The number of H-bridges required for an nlevel inverter are N = (n-1)/2. Single-phase structure of the five level cascaded Hbridge inverter is shown in Fig. 1. The output phase voltage is equal to the summation of the output of the each H-bridge module as below.

1. N.Rajavinu, M.E Research scholar

St.Peter's University

$Vac = Vdc/2 + Vdc/2 + \dots + Vmh$ (1)

Where h is the number of H-bridge modules used in the multilevel circuit.

Figure.1. Cascaded 5 level MLI

| Sal | S <sub>bl</sub> | Sd | Sdl | Sa | Sb | Sc | Sd | Vac                 |

|-----|-----------------|----|-----|----|----|----|----|---------------------|

| 0   | 1               | 1  |     | 1  | 0  |    | 1  |                     |

|     | 1               | 1  | 0   | 1  |    | 0  | 1  | V <sub>dc</sub>     |

| 0   | 1               | 1  | 0   | 1  | 0  | -  | 0  | V <sub>dc</sub> /2  |

| 0   | 0               | 0  | 0   | 0  | 0  | 0  | 0  | 0                   |

| 1   | 0               | 0  | 1   | 1  | 0  | 1  | 0  | -V <sub>dc</sub> /2 |

| 1   | 0               | 0  | 1   | 0  | 1  | 1  | 0  | -V <sub>dc</sub>    |

Table.1 Switching Pattern of five level inverter

Each module of the H-bridge has its own input voltage and consists of four switching power devices; Sa, Sb, Sc, and Sd .Each module of the cascaded multilevel inverter can produce three levels of the output voltage which is +V, 0 and -V. This is made possible by connecting the DC sources sequentially to the AC side via four power devices. For example cascaded H-bridge multilevel inverter with four modules of the H bridge will produce nine levels of the output phase voltage.

The cascaded H Complete bridge multilevel inverter has several advantages because of its simple and modular circuit configuration. Each of its modules is identical and incorporates both input and output circuitry. Besides, the cascaded H-bridge multilevel inverter requires the least number of components compared to other types of multilevel inverter. These features provide flexibility in extending cascaded H-bridge multilevel inverter to higher number of levels without modification on the circuit itself.

#### III.PWMCONTROL OF MULTILEVEL INVERTER

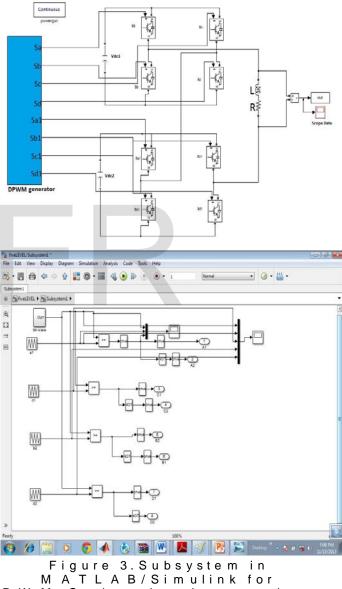

The technique uses comparison of different carrier signals with the sinusoidal signal. The saw tooth waves as a carrier signals are used and generated by toolbox of the MATLAB/SIMULINK.

The power switch is usually of MOSFET or IGBT. . The modulation index is defined as:  $M \square Vm / 2Vc$  (2)

Where  $V_m$  is the peak value of digital sinusoidal wave and  $V_c$  is the carrier peak value [12]

Figure.2 Simulation of Single Phase Five Level Multilevel Inverter

PWM Gating signal generation.

### SIMULATION RESULTS

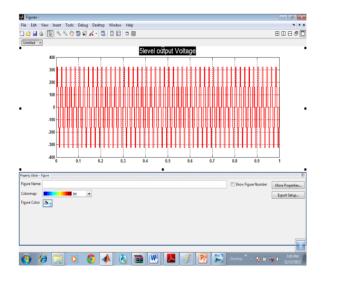

The proposed five-level cascaded multilevel PWM single phase inverter is simulated by using MATLAB/Simulink. The different levels of the carrier signals (such as saw tooth signals) are compared with the sinusoidal (reference signal). Each saw tooth signal is of the same amplitude and same frequency of 1 kHz that is generated from the upcounter. The output voltage waveform of five-level cascaded H-bridge inverter has been simulated and shown in figure 4

Figure .4.output voltage waveform of five-level cascaded Hbridge inverter

## V. CONCLUSION

The FPGA based digital control switching patterns are adopted and applied to the cascaded multilevel inverter switches to generate multilevel output voltages. The FPGA reduces complexity, increases speed and adds flexible in the design of the control circuit for hardware implementation. It can efficiently extend the range of modulation index which facilitates a better quality output voltage with minimal distortion. The experimental, simulation and hardware implementation results demonstrate the improved quality voltage waveform shapes at the output of the inverter. The main objective of this thesis is to provide a general notion about the multilevel power converters and various modulation strategies mainly PWM techniques and their applications.

#### VI. References

- J.S. Lai and F.Z.Peng, Multilevel converters –"A new breed of power conversion "IEEE Transaction. on Industrial Application., vol.32, pp. 509-517, May/June. 1996.

- [2] J. Rodriguez, Jih-Sheng Lai and F. Z. Peng. Multilevel Inverters: A Survey of Topologies, Controls, and Applications. IEEE Transaction on Industrial Electronics. 49(4), pp.724-738,2002,.

- [3] L. G. Franquelo,J.Rodríguez, Jose I. leon,S. kouro, R. portillo and maria a.m. Prats. "The Age Of Multilevel Inverters Arrives". IEEE Industrial Electronics Magazine, pp1932-4529,June 2008,.

- [4] S. C. Huerta, A. Castro, O. Garcia, J. A. Cobos, "FPGABased Digital Pulsewidth Modulator With Time Resolution Under 2 ns", IEEE transactions on power electronics, vol. 23, no. 6, November 2008.

- [5] M. Veenstra and A. Rufer, "PWM-control of multilevel voltage-source inverters," in Proc. IEEE 31st Annu. PESC, Galway, Ireland, , vol. 3, pp. 1387–1393, Jun. 18–23, 2000.

- [6] A. Gupta and A. Khambadkone, "A space vector PWM scheme for multi-level inverters based on two-level space vector PWM," IEEE Transaction on. Industrial .Electron., vol. 53, no. 5, pp. 1631–1639, Oct. 2006.

- [7] N. D. Patel, U. K. Madawala." A Bit-Stream-Based PWM Technique for Sine-Wave Generation". Industrial Electronics, IEEE Transactions, vol. 56, No. 7, July 2009

- [8] E. Roberto C. Da Silva, E. Cipriano Dos Santos, Jr., And Cursino Branda "O Jacobina," Nonsinusoidal Carrier-Based PWM and Space Vector Modulation Techniques". IEEE Industrial Electronicsmagazine. pp1932-4529, June 2011.

- [9] Peter Bishop, "A tradeoff between microcontroller, DSP, FPGA and ASIC technologies", EE Times design Feb 2009

- [10] J. J. Rodriguez-Andina, M. J. Moure, and M. D. Valdes, "Features, design tools, and application domains of FPGAs," IEEE Trans. Ind. Electron., vol. 54, no. 4, pp. 1810–1823, Aug. 2007.

- [11] Khanchai , Krissanapong , Sirichai and V. Monyakul, "Comparison Between FPGA-Based and DSP IC-Based Islanding Detection for Grid Connected Inverter in a Photovoltaic System", International Conference on Control, Automation and Systems 2007,Oct. 17-20,2007 in COEX, Seoul, Korea

- [12] S. Mekhilef and Masaoud "Xilinx FPGA Based Multilevel PWM Single Phase Inverter" Engineering e-Transaction, Vol.1, No 2, pp 40-45, 2006

- [13] E. Monmasson and M. N. Cirstea, "FPGA design methodology for industrial control systems—A review," IEEE Transaction on. Industrial. Electron., vol. 54,no. 4, pp. 1824–1842, Aug. 2007

- [14] S. Karimi, P. Poure2, Y. Berviller And S. Saadate," A Design Methodology for Power Electronics Digital Control based on an FPGA in the Loop Prototyping". Proceedings of 14th IEEE International Conference on Electronics, Circuits and Systems, 2007. ICECS 2007,IEEE 2007 [15] M.I. Ahmad,Z. Husin,R. B. Ahmad,H. A Rahim,M.S. Abu Hassan,M.N. Md Isa "FPGA based control IC for MultilevelInverter" Proceedings of the International Conference on Computer and Communication Engineering 2008.

- [16] D. Puyal, L. A. Barragán, Jesús Acero, José M. Burdío,Ignacio Millán. "An FPGA-Based Digital Modulator for Full- or Half-Bridge Inverter Control", IEEE transactions on power electronics, vol. 21, no. 5, September 2006.